# 日 JAPAN PATENT OFFICE

別紙添付の書類に記載されている事項は下記の出願書類に記載されている事項と同一であることを証明する。

This is to certify that the annexed is a true copy of the following application as filed with this Office.

出願年月日 Date of Application:

2003年 9月12日

出 願 番 Application Number:

特願2003-322170

[ST. 10/C]:

[JP2003-322170]

出 Applicant(s):

人

大見 忠弘

2003年11月25日

特許庁長官 Commissioner, Japan Patent Office

【書類名】

特許願

【整理番号】

M-1163

【提出日】平成15年 9月12日【あて先】特許庁長官殿【国際特許分類】H01L 21/304

【発明者】

【住所又は居所】 宮城県仙台市青葉区米ケ袋2-1-17-301

【氏名】 大見 忠弘

【発明者】

【住所又は居所】 宮城県仙台市宮城野区平成1丁目1番地22号 コーポ丹野K6

【発明者】

【住所又は居所】 神奈川県横浜市旭区さちが丘148-4-701

【氏名】 赤堀 浩史

【特許出願人】

【識別番号】 000205041【氏名又は名称】 大見 忠弘

【代理人】

【識別番号】 100071272

【弁理士】

【氏名又は名称】 後藤 洋介

【選任した代理人】

【識別番号】 100077838

【弁理士】

【氏名又は名称】 池田 憲保

【手数料の表示】

【予納台帳番号】 012416 【納付金額】 21,000円

【提出物件の目録】

【物件名】 特許請求の範囲 1

【物件名】

明細書 1

【物件名】

図面 1

【物件名】

要約書 1

【包括委任状番号】

0303948

# 【書類名】特許請求の範囲

### 【請求項1】

シリコン半導体表面を等方性酸化手段で酸化し犠牲酸化膜を形成する第1の工程と、前記犠牲酸化膜を剥離する第2の工程とを含み、前記第1および第2の工程を少なくとも1回経ることによって前記シリコン半導体表面を平坦化させ、該平坦化した表面を有するシリコン半導体を用いて半導体デバイスを形成することを特徴とする半導体装置の製造方法

# 【請求項2】

チャネル領域となるべきシリコン半導体表面を等方性酸化手段で酸化し犠牲酸化膜を形成する第1の工程と、前記犠牲酸化膜を剥離する第2の工程とを含み、前記第1および第2の工程を少なくとも1回経ることによって前記チャネル領域となるべきシリコン半導体表面を平坦化させ、該平坦化したチャネル領域となるべきシリコン半導体表面上にゲート絶縁膜を形成することを特徴とする半導体装置の製造方法。

### 【請求項3】

前記第1の工程と前記第2の工程とを2回以上繰り返すことを特徴とする請求項1または2記載の半導体装置の製造方法。

# 【請求項4】

前記等方性酸化手段は、400℃以下の温度で前記シリコン半導体表面をラジカル酸化する手段であることを特徴とする請求項1乃至3のいずれか1に記載の半導体装置の製造方法。

# 【請求項5】

前記等方性酸化手段は、前記シリコン半導体表面をオゾン水に接触させる手段であることを特徴とする請求項1乃至3のいずれか1に記載の半導体装置の製造方法。

## 【請求項6】

前記等方性酸化手段は、前記シリコン半導体表面を過酸化水素水を含む水溶液に接触させる手段であることを特徴とする請求項1乃至3のいずれか1に記載の半導体装置の製造方法。

### 【請求項7】

前記オゾン水は、超純水に0.001ppm乃至100ppmのオゾンが溶存する水であることを特徴とする請求項5に記載の半導体装置の製造方法。

## 【請求項8】

前記オゾン水は、超純水に1ppm乃至30ppmのオゾンが溶存する水であることを 特徴とする請求項5に記載の半導体装置の製造方法。

#### 【請求項9】

前記過酸化水素水は、30万至100重量%の過酸化水素を含むことを特徴とする請求項6に記載の半導体装置の製造方法。

# 【請求項10】

前記等方性酸化手段の前記接触は、10乃至30℃で20秒以上行うことを特徴とする請求項5乃至9のいずれか1に記載の半導体装置の製造方法。

## 【請求項11】

前記第2の工程は、フッ酸を含む水溶液を用いて前記犠牲酸化膜を剥離する工程を有することを特徴とする請求項1乃至10のいずれか1に記載の半導体装置の製造方法。

#### 【請求項12】

前記第2の工程は、塩酸とフッ酸の混合溶液を用いて前記犠牲酸化膜を剥離する工程を 有することを特徴とする請求項1乃至10のいずれか1に記載の半導体装置の製造方法。

### 【請求項13】

前記第2の工程は、HFと溶存酸素濃度が100ppb以下のH2Oとを含有する溶液を用いて前記犠牲酸化膜を剥離する工程を有することを特徴とする請求項1乃至10のいずれか1に記載の半導体装置の製造方法。

### 【請求項14】

前記シリコン半導体表面は、実質的に(110)面方位を有することを特徴とする請求項1乃至13のいずれか1に記載の半導体装置の製造方法。

# 【請求項15】

前記シリコン半導体表面は、(110)面、(551)面、(311)面、(221)面、(553)面、(335)面、(112)面、(113)面、(115)面、(117)面、(331)面、(332)面、(111)面および(320)面のいずれかの方位を有することを特徴とする請求項1乃至14のいずれか1に記載の半導体装置の製造方法。

# 【請求項16】

前記第1の工程から前記半導体装置の形成まで、前記シリコン半導体表面を空気に触れさせないようにしたことを特徴とする請求項1乃至15のいずれか1に記載の半導体装置の製造方法。

# 【請求項17】

前記第1および第2の工程において用いられる薬液を空気に触れさせないようにしたことを特徴とする請求項5万至16のいずれか1に記載の半導体装置の製造方法。

# 【請求項18】

シリコン半導体表面を等方性酸化手段で酸化し犠牲酸化膜を形成する第1の工程と、前記犠牲酸化膜を剥離する第2の工程とを含み、前記第1および第2の工程を少なくとも1回経ることによって前記シリコン半導体表面を平坦化させることを特徴とする半導体表面の平坦化方法。

# 【請求項19】

前記第1の工程と前記第2の工程とを2回以上繰り返すことを特徴とする請求項18記載の半導体表面の平坦化方法。

# 【請求項20】

前記等方性酸化手段は、400℃以下の温度で前記シリコン半導体表面をラジカル酸化する手段であることを特徴とする請求項18または19に記載の半導体表面の平坦化方法

### 【請求項21】

前記等方性酸化手段は、前記シリコン半導体表面をオゾン水に接触させる手段であることを特徴とする請求項18または19に記載の半導体表面の平坦化方法。

# 【請求項22】

前記等方性酸化手段は、前記シリコン半導体表面を過酸化水素水を含む水溶液に接触させる手段であることを特徴とする請求項18または19に記載の半導体表面の平坦化方法

#### 【請求項23】

シリコン半導体表面を等方性酸化して犠牲酸化膜を形成する等方性酸化手段と、前記犠牲酸化膜を剥離する剥離手段とを含むことを特徴とする半導体製造装置。

## 【請求項24】

請求項乃1至17のいずれか1に記載の製造方法によって製造された半導体装置。

# 【書類名】明細書

【発明の名称】半導体装置の製造方法

## 【技術分野】

# [0001]

本発明は、平坦な半導体表面を有する半導体装置の製造法方に関し、特に平坦な半導体 表面を有するシリコン半導体装置の製造方法、シリコン半導体表面の平坦化方法、表面平 坦化処理を実行する半導体製造装置、および前記表面処理を行うことによって得られた半 導体デバイス等の製品に関する。

### 【背景技術】

# [00002]

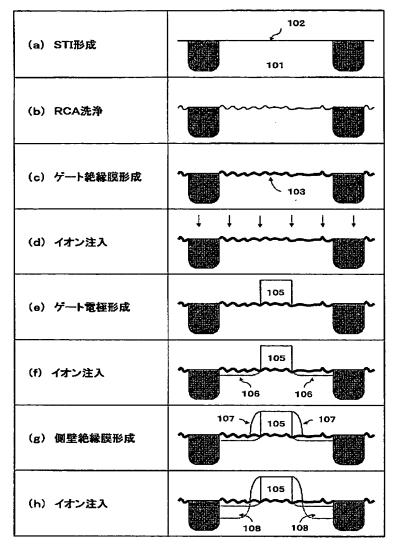

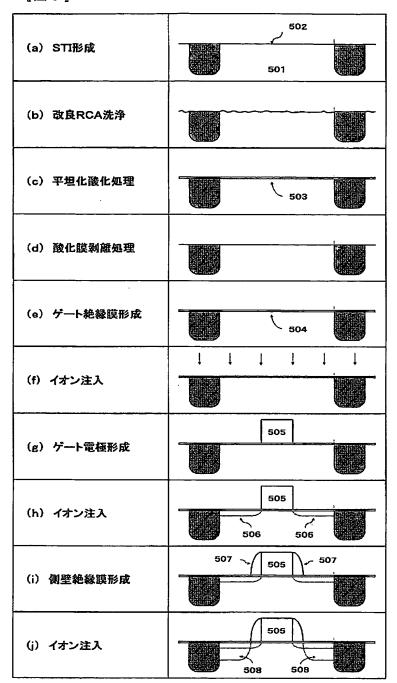

従来の半導体領域に形成された集積回路を構成する電界効果トランジスタの製造工程を、LDD (Lightly Doped Drain)構造のn型電界効果トランジスタを例にし、図1を用いて説明する。

# [0003]

まず、半導体基板であるp型(100)面シリコン101の表面に、例えばSTI(Shallow Trench Isolation)法により素子分離を行い、素子領域102を形成する(a)。

### [0004]

なお本発明における面方位の記述として、例えば(100)は、(100)面に等価な面(100)、(010)、(001)など全てを総称して表している。

# [0005]

素子領域102に、RCA洗浄処理を行い(b)、有機物、パーティクル、メタル不純物を除去した後、ゲート絶縁膜(SiO2)103を形成する(c)。

## [0006]

次に、シリコン101の全面に、しきい値電圧を制御するため、ボロンをイオン注入する(d)。

### [0007]

次に、シリコン101の全面に、多結晶シリコン膜を堆積させ、これをパターニングして素子領域102のゲート絶縁膜103上に、多結晶シリコン電極105を形成する(e)。

## [00008]

次にリンを低濃度でイオン注入して高電界を緩和するn-ソース及びドレイン領域106を形成する。

#### [0009]

次に、CVD法などにより、ゲート電極105を被覆するように、シリコン酸化膜(SiO2)を、シリコン101の全面に堆積させ、異方性エッチングを行って、ゲート電極105の側壁に側壁絶縁膜107を形成する(g)。

#### [0010]

その後、砒素などのn型不純物を高濃度にイオン注入してn+y-z及びドレイン領域 108 を形成する (h)。

### 【発明の開示】

【発明が解決しようとする課題】

#### (0011)

しかしながら、上記のような電界効果トランジスタ形成方法の場合、RCA洗浄におけるアルカリ処理時、並びに純水リンス時等に、素子領域102表面を荒らしてしまう。この荒れたシリコンとゲート絶縁膜界面を用いて電界効果トランジスタを作製すると、トランジスタの駆動能力が低下するのみならず、実際にゲート電極に電圧を加えた場合、突起部に電界集中を生じ、絶縁破壊に至りやすくなることは良く知られている。

### [0012]

特に、(110)シリコンを用いた場合、アルカリ処理時における荒れは激しくなる。

現在、LSI作製には、主に(100)シリコンが用いられているが、n型電界効果トランジスタと比較し、p型トランジスタの駆動能力、つまり移動度が約0.3倍と低いことが問題視されている。対して(110)シリコンを用いた場合、p型トランジスタの駆動能力は、(100)の場合と比較し、約2.5倍も上昇するメリットがある。しかしながら、n型トランジスタの駆動能力は、(100)の場合と比較し、逆に約0.6倍と低下してしまう。n型トランジスタの駆動能力の低下が抑えられれば、(110)シリコンは、非常に有用な材料となり得る。(110)シリコンにおいて、n型トランジスタの駆動能力低下を抑える為には、シリコンとゲート絶縁膜界面のラフネスを低減させれば良いことが推測される。

## $[0\ 0\ 1\ 3]$

以上はn型電界効果トランジスタを例として説明したが、TFT、CCDやIGBT等の半導体素子についても、同様なことが言える。

# $[0\ 0\ 1\ 4]$

以上のような問題から、先に提出した出願(2002年特許願第350177号)では、ラジカル酸化を用いることによる平坦化、湿式酸化を繰り返すことによる平坦化について述べられている。ラジカル酸化を用いる手法は、プラズマ中で酸素ラジカルを含む雰囲気で、400℃以下の温度で半導体領域の表面に犠牲酸化膜を形成し、その後、犠牲酸化膜を剥離することにより平坦化を実現している、非常に効果的な手法である。しかし、犠牲酸化膜形成工程が真空装置で行われるであるのに対し、犠牲酸化膜剥離工程が主に薬液処理装置で行われる。その場合、それぞれ別装置で処理が成されるということで、スループットが低下するという問題がある。同じことは湿式酸化と薬液によるエッチバックを繰り返すことにより平坦化する手法についても言える。これらの方法は、経験的に表面が平坦化するという知見のもとになされたものであるが、なぜ平坦化するかという原因は知られていなかった。

# [0015]

本発明は、このような事情によりなされたものであり、犠牲酸化膜の形成および剥離によるシリコン表面平坦化の原因を解明して、より効率的、目的論的な平坦化方法を提供することを目的とする。

# [0016]

本発明の他の目的は、液処理装置のみを用いて短時間に半導体領域表面を平坦化することができる方法を提供することにある。

### [0017]

本発明の更に他の目的は、チャンネル領域とゲート絶縁膜界面のラフネスを低減させることにより、駆動力が向上した半導体装置及びその製造方法を提供することにある。

#### 【課題を解決するための手段】

# [0018]

本発明は、半導体領域とゲート絶縁膜界面のラフネスを低減させることにより、半導体装置におけるキャリア電子の散乱を低く抑え、半導体装置のキャリア電子駆動能力を向上させることに特徴がある。半導体装置のキャリア電子移動度は、半導体領域表面のラフネスと密接な関係を持つ。

### [0019]

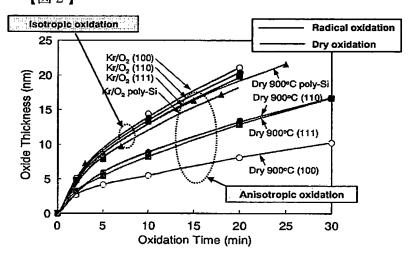

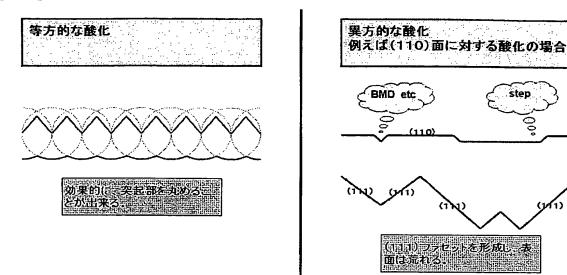

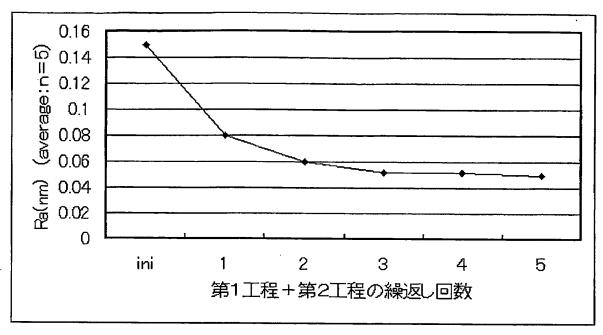

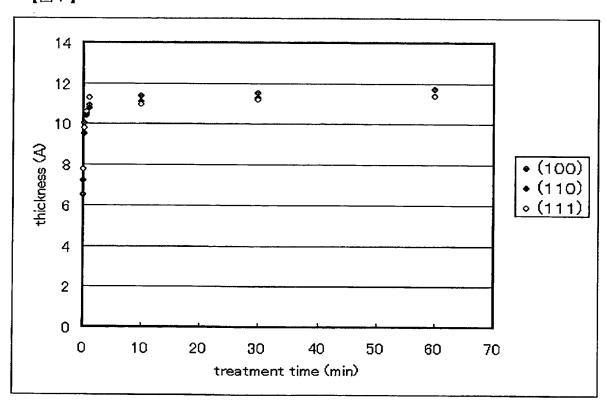

犠牲酸化により平坦化を行う手法において、重要な指針としては、等方的な酸化を行えるか否かであることが判明した。図2にラジカル酸素による酸化と、ドライO2による酸化を行った際の、酸化時間と膜厚の関係を示す。なお酸化は、シリコン(100)、(110)、(111)面に対して行っている。ドライ酸化は、シリコン面方位により酸化レートが異なるのに対し、ラジカル酸化の場合、面方位によらず酸化レートは同じである。これはラジカル酸化によって、等方的な酸化が行われること、それに対してドライ酸化では異方的な酸化が行われることを示している。等方的及び異方的な酸化を行った際の(110)表面の平坦性に与える影響を、図3に示した。等方的な酸化の場合、表面に細かな凹凸があっても酸化が等方的に進行するため、細かな突起が効果的に除去されて、平坦化

される様子が分かる。これに対して、異方的な酸化の場合、特定の面のみに選択的に酸化が進行し、BMD(バルクマイクロディフェクト)や原子ステップをトリガとして、表面を荒らして行く様子が分かる。つまり、シリコンなどの結晶体に対し、酸化により平坦化を行う場合、その面方位によらず、等方的な酸化を行うことが大事であることが分かる。

# [0020]

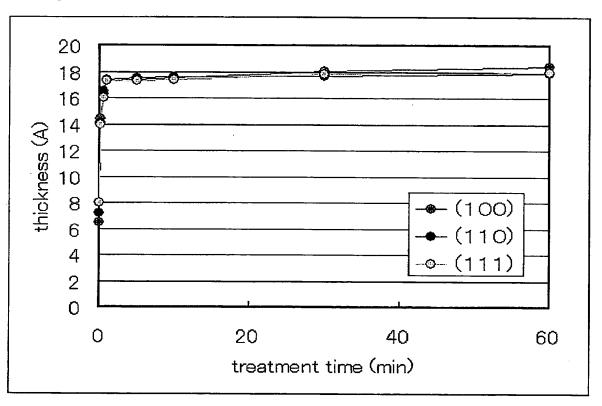

本発明者等は、鋭意実験の結果、オゾン水または過酸化水素水を用いても、このような等方的な酸化を行えることを新たに見出した。図4に、オゾン水をシリコン表面に接触(以下、接触とはシリコンを薬液に浸漬すること、および薬液をシリコン表面に流したり吹き付けたりすることを含む)させた際の、処理時間と酸化膜厚の関係を示す。オゾン水としては超純水に5ppmのオゾンが溶存しているものを用い、処理は室温(23 $\mathbb C$ )で行った。図2と同様に、シリコン(100)、(110)、(111)面方位に対して行った結果、面方位に関係なく酸化が進行していること、すなわち、等方的な酸化が行われていることが判明した。さらに、30秒程度のオゾン水処理により、酸化膜厚が飽和し、それ以上酸化が進まないことが分かる。これは、犠牲酸化膜の形成時間が30秒程度あれば、十分であることを意味し、極めて短時間で平坦化処理が可能となり、枚葉装置化を容易に実現することができる。後に述べるように、過酸化水素を含む水溶液を用いても同様の結果が得られた。

# [0021]

特に、実質的に(110)面方位をその表面に有するシリコンでは、異方的な酸化が行われる場合、(111)面が優先的に酸化されることにより、<-110>方向に溝が形成され易いことが知られている。ラジカル酸化、オゾン水、過酸化水素水のような等方的な酸化手段を用いて犠牲酸化膜を形成し、剥離することによる平坦化手法は、実質的に(110)面方位を表面に有するシリコンの平坦化に特に有効である。

# [0022]

なお実質的な(110)面方位とは、結晶学的に見て、(110)面方位とほぼ等価な方向を向いている面であり、(551)面、(311)面、(221)面、(553)面、(335)面、(112)面、(113)面、(115)面、(117)面などを含む

# [0023]

またKazuo Satoら報告のSensors and Actuators 7 3(1999) P122-130におけるFig.2 より、(110) 面をアルカリエッチング処理した場合、<-110>方向に筋が走る表面形状が得られることが分かっている。(110) 面と同様な表面形状が得られる領域として、<100>方向に $0\sim12$ ° までオフさせた面、例えば8° オフの (551) 面などが当てはまる。<-110>方向へは1° オフさせた面までは、同様な表面形状が得られる。本Fig.2の (110) 面と同じ表面ラフネス挙動を示す面方位を選んでも良い。

### [0024]

さらにT. Satoら報告のPhys. Rev., B4, 1950 (1971) によると、 (110) 面と同様なキャリア電子移動度が得られる面を知ることが出来る。それにより、<-110>方向に電子を流した場合、<-110>方向へ $0\sim35^\circ$  オフさせた面、例えば (331) 面、 (221) 面、 (332) 面、 (111) 面などを用いても (110) 面と同様の電子移動挙動を得ることが出来る。また<1-10>方向へ $0\sim12^\circ$  オフさせた面、例えば (320) 面を用いても (110) 面と同様の挙動を得ることが出来る。以上の面やその近傍面を選んでも良い。

## [0025]

本発明の特徴は次の通りである。

# [0026]

請求項1に示した本発明の半導体装置の製造方法は、シリコン半導体表面を等方性酸化 手段で酸化し犠牲酸化膜を形成する第1の工程と、前記犠牲酸化膜を剥離する第2の工程 とを含み、前記第1および第2の工程を少なくとも1回経ることによって前記シリコン半 導体表面を平坦化させ、該平坦化した表面を有するシリコン半導体を用いて半導体デバイスを形成することを特徴とする。

# [0027]

請求項2の半導体装置の製造方法は、チャネル領域となるべきシリコン半導体表面を等方性酸化手段で酸化し犠牲酸化膜を形成する第1の工程と、前記犠牲酸化膜を剥離する第2の工程とを含み、前記第1および第2の工程を少なくとも1回経ることによって前記チャネル領域となるべきシリコン半導体表面を平坦化させ、該平坦化したチャネル領域となるべきシリコン半導体表面上にゲート絶縁膜を形成することを特徴とする。

### [0028]

前記第1の工程と前記第2の工程とは2回以上、好ましくは3回またはそれ以上繰り返すことが好ましい。

# [0029]

前記等方性酸化手段は、400℃以下の温度で前記シリコン半導体表面をラジカル酸化する手段、または前記シリコン半導体表面をオゾン水に接触させる手段、または前記シリコン半導体表面を過酸化水素水を含む水溶液に接触させる手段とすることができる。

# [0030]

前記オゾン水は、超純水に0.001ppm乃至100ppm、好ましくは1ppm乃至30ppmのオゾンが溶存する水であればよい。また前記過酸化水素水は、30乃至100重量%の過酸化水素を単独または硫酸等と混合して含むものであってよい。前記等方性酸化手段の前記接触は、10乃至30℃、好ましくは20℃から30℃で20秒以上、好ましくは30秒以上行うことが望ましい。

# [0031]

前記第2の工程は、フッ酸を含む水溶液を用いて前記犠牲酸化膜を剥離する工程を有していてよい。フッ酸は、濃度が0.01%乃至1.0%、好ましくは0.1%から1.0%、さらに好ましくは0.5%程度、のものを用いることができる。また、前記第2の工程は、塩酸とフッ酸の混合溶液を用いて前記犠牲酸化膜を剥離する工程であってもよい。この場合、フッ酸は濃度10%乃至30%、塩酸は残余、すなわち90%乃至70%とするのが好ましい。また前記第2の工程は、HFと溶存酸素濃度が100ppb以下のH20とを含有する溶液を用いて前記犠牲酸化膜を剥離する工程であってもよい。

# [0032]

前記シリコン半導体表面は、(100)面や(111)面のものであってもよいが、実質的に(110)面方位を有するものに特に効果がある。実質的に(110)面は、(110)面、(551)面、(311)面、(221)面、(553)面、(335)面、(112)面、(113)面、(115)面、(117)面、(331)面、(332)面、(111)面および(320)面のいずれかの方位を含む。

## [0033]

前記第1の工程から前記半導体装置の形成まで、前記シリコン半導体表面を空気に触れさせないようにすること、前記第1および第2の工程において用いられる薬液を空気に触れさせないようにすることが好ましい。

# 【発明の効果】

# $[0\ 0\ 3\ 4]$

オゾン水、過酸化水素水、またはラジカル酸化による等方性酸化手段による犠牲酸化膜 形成と犠牲酸化膜の剥離処理を行うことで、シリコン表面の平坦性を、Ra=0.05 n mまで低下させることが出来た。本技術は、処理時間が短く、生産性が高いものである。 シリコン表面とゲート絶縁膜界面が原子的に平坦であることから、キャリア移動度の向上 に加え、ゲート絶縁膜の信頼性も向上する。

# 【発明を実施するための最良の形態】

# [0035]

p型(110)シリコン501の表面に、例えばSTI(Sallow Trench Isolation)法により素子分離を行い、ソース、ドレイン及びチャネル領域を 含む素子領域502を形成する(a)。

# [0036]

素子領域302に対し、有機物、パーティクル、メタル汚染除去の為、RCA洗浄を施す(b)。なおRCA洗浄中の一工程であるSC1洗浄時において、シリコン表面のエッチングによりラフネス増加が懸念される。そこでOH濃度が低いSC1洗浄処理を施す。典型的なSC1処理では、NH4OH:H2O2:H2〇=1:1:5の薬液を用いるが、ここでは、NH4OH:H2O2:H2〇=1:1:5の薬液を用いるが、ここでは、NH4OH:H2O2・H2〇=0・05:1:5と、OH濃度を下げている。なお、ここで、シリコン結晶中において、COP等の欠陥密度が高い場合、SC1処理時に表面ラフネスの増加を加速する。さらには、欠陥が原因で、SC1処理後にマイクロピットが表面に形成され、酸化膜耐圧の劣化も誘発する。特にCZウェハを用いた場合、COP密度が高い。従って、SC1洗浄時における表面ラフネスの増加を抑制するには、OP密度が高い。従って、SC1洗浄時における表面ラフネスの増加を抑制するには、好ましくは、水素アニール処理またはアルゴンアニール処理等を施し、残留酸素のレベルを、5E16/cm3程度まで低下させたシリコンを用いるか、さらにはSiエピタキシャル成長を表面に施したシリコンウェハを用いた。

# [0037]

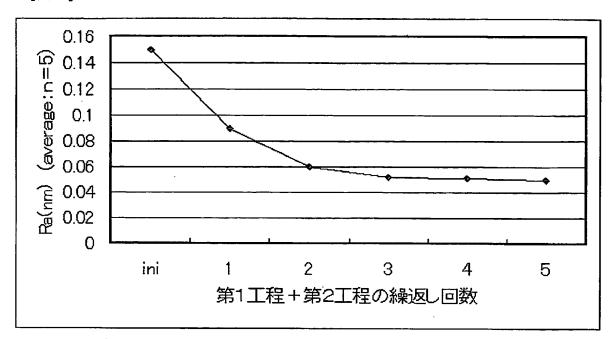

なお、前記低OH濃度のSC1工程を用いても、依然、中心線平均粗さRaが0.15 nm程度ある。

# [0038]

そこで、素子領域のシリコン表面の平坦化処理として、オゾン水にシリコン表面を浸し、犠牲酸化膜503を形成(図5(c))。その後、水素添加水を用いて希釈した0.5% HF溶液を用い、犠牲酸化膜を剥離した(図5(d))。その犠牲酸化膜の形成と剥離の工程を、5回繰り返した。オゾン水に浸した時間は30秒、犠牲酸化膜剥離時間は30秒であり、5回の繰り返しにかかった時間は、わずか5分である。結果、中心線平均粗さRaが0.05nmと低減した。これは特願2002年第350177号と同等レベルの平坦性であるが、本願の方が、処理にかかった時間が格段に短く、生産性に優れていると言える。

### [0039]

ここで、さらに第1工程と第2工程の繰り返し回数と平坦性との関係を調べた。図6は、横軸が繰り返し回数、縦軸は中心線平均粗さRaである。図に示すように繰り返し3回を超えると、ほぼ飽和の傾向が見られ、繰り返し回数には適正値があることが確認出来た

# [0040]

なお、等方的な酸化手段として、過酸化水素水や過酸化水素水の水溶液、例えば、硫酸と過酸化水素水の混合液を用いても、等方的な酸化が行える。図7に、硫酸と過酸化水素水を4:1の比で混合した溶液(SPM)にシリコン表面を浸した際の、溶液処理時間と酸化膜厚の関係を示す。図4と同様に、シリコン(100)、(110)、(111)面方位に対して行っている。図7に示すように、この手段によっても、等方的な酸化が行われ、表面平坦化に対し、有効である。さらに、30秒程度のSPM処理により、酸化膜厚が飽和し、それ以上酸化が進まないことが分かる。これは、犠牲酸化膜の形成時間が30秒程度あれば充分であること、短時間の処理による表面平坦化、ひいては枚葉装置の実現に等方性酸化手段が有効であることを示している。

#### [0041]

さらに第1工程にSPM溶液を用い、第2工程に希釈した0.5%HF溶液を用いた際、第1工程と第2工程の繰り返し回数と平坦性との関係を調べた。図8は、横軸が繰り返し回数、縦軸は中心線平均粗さRaである。結果、図6のオゾン水の場合と同様、繰り返し3回を超えると、ほぼ飽和の傾向が見られ、繰り返し回数には適正値があることが確認出来た。

# [0042]

犠牲酸化膜の剥離工程においては、低〇H濃度の薬液、例えば、HFとHCIの混合溶 出証特2003-3097179 液を用いても、OHによるSi表面エッチングが抑制されることから、更なる平坦化効果が期待できる。

# [0043]

本発明による等方性酸化処理を用いたシリコン表面の平坦化は、シリコン面方位や適応される半導体素子に限定されること無く、応用が可能な技術である。

### $[0\ 0\ 4\ 4\ ]$

次に、素子領域のシリコン表面を酸化し、5 n mのゲート絶縁膜(SiO2)504を 形成する(e)。なお本発明において形成されるシリコン酸化膜は、少なくともシリコン と接する部分に存在すればよく、その上層に異種の材料、アルカリ土類金属、希土類金属 、遷移金属を用いた酸化物、窒化物、酸窒化物、シリケートなどが1層以上積層形成され た絶縁膜を用いても良い。また本発明において形成されるシリコン酸化膜の代わりに、ア ルカリ土類金属、希土類金属、遷移金属を用いた酸化物、窒化物、酸窒化物、シリケート などの単層または積層構造を用いても良い。さらには、シリコン酸化膜、シリコン窒化膜 、シリコン酸窒化膜の何れか一つ以上を含む膜を用いても良い。

# [0045]

次に、シリコン 501 の全面に、しきい値電圧を制御するため、ボロンをイオン注入する (f)。

# [0046]

次に、シリコン 5 0 1 の全面に、多結晶シリコン膜を堆積させ、これをパターニングして素子領域 5 0 2 のゲート絶縁膜 5 0 4 上に、多結晶シリコン電極 5 0 5 を形成する( g )。

# [0047]

次にリンを低濃度でイオン注入して高電界を緩和する n - ソース及びドレイン領域 5 0 6 を形成する (h)。

# [0048]

次に、CVD法などにより、ゲート電極305を被覆するように、シリコン酸化膜(SiO2)を、シリコン501の全面に堆積させた後、異方性エッチングを行って、ゲート電極505の側壁に側壁絶縁膜507を形成する(i)。

### [0049]

その後、砒素などのn型不純物を高濃度にイオン注入してn+y-z及びドレイン領域 5 0 8 を形成する(j)。

# 【図面の簡単な説明】

#### [0050]

- 【図1】従来技術における電界効果トランジスタの作製フローである。

- 【図2】酸化時間と酸化膜厚の関係を示すグラフである。

- 【図3】等方的な酸化と異方的な酸化が平坦性に及ぼす挙動を説明する模式図である

- 【図4】オゾン水による処理時間と酸化膜厚の関係ほを示すグラフである。

- 【図5】本発明に係る実施例における電界効果トランジスタの作製フローを示す図である。

- 【図6】第1工程と第2工程の繰り返し回数とRaとの関係を示すグラフである。

- 【図7】SPMによる処理時間と酸化膜厚の関係を示すグラフである。

- 【図8】第1工程と第2工程の繰り返し回数とRaとの関係を示すグラフである。

# 【符号の説明】

# $[0\ 0\ 5\ 1]$

| 5 0 1 | シリコン         |

|-------|--------------|

| 5 0 2 | 素子領域         |

| 5 0 3 | 犠牲酸化膜        |

| 5 0 4 | ゲート絶縁膜(SiO2) |

| 5 0 5 | 多結晶シリコンゲート電極 |

| 5 0 6 | n ーソース及びドレイン領域 |

|-------|----------------|

| 5 0 7 | 側壁絶縁膜          |

| 5 0 8 | n+ソース及びドレイン領域  |

【書類名】図面【図1】

【図2】

【図3】

# 【図4】

【図5】

【図6】

【図7】

【図8】

【書類名】要約書

【要約】

【課題】 犠牲酸化膜を形成し、これを剥離することによってシリコン基板の表面を平 坦化する手法を改善し、より平坦なシリコン表面を形成することである。

【解決手段】 シリコン基板表面を等方性酸化により犠牲酸化膜を形成し、等方性酸化によって形成された酸化膜を剥離することによって、平坦度の高い表面が得られる。等方性酸化の手法として、オゾン水、過酸化水素水を使用しても良いし、ラジカル酸化を用いても良い。

【選択図】 図5

特願2003-322170

出願人履歴情報

識別番号

[000205041]

変更年月日

変更理由]

1990年 8月27日

住 所 氏 名 新規登録 宮城県仙台市青葉区米ケ袋2-1-17-301

大見 忠弘